# Development of a universal bidirectional galvanic isolated switch module for power converter applications

# Kopano Mokhalodi 20403810

A dissertation submitted in fulfilment of the requirements for the Magister Technologiae: Engineering: Electrical

Department: Electronic Engineering

Faculty of Engineering and Technology

Vaal University of Technology

Vanderbijlpark

Supervisor: Dr JF Janse van Rensburg

Date: June 2013

### **Declaration**

I, Kopano Mokhalodi, hereby declare that the following research information is solely my own work. This is submitted for the requirements of the Magister Technologiae: Engineering: Electrical to the Department of Electronics and Engineering at the Vaal University of Technology, Vanderbijlpark. This work has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree.

| Mokhalodi Kopano |  |

|------------------|--|

|                  |  |

| Date:            |  |

## Acknowledgements

I hereby wish to express my gratitude to:

- Prof H C vZ Pienaar for his continued encouragement and guidance.

- Dr JF Janse van Rensburg for his wisdom and contribution that helped me.

- Personnel of the Department of Applied Electronics and Electronic Communication Telkom Centre of Excellence and my fellow colleagues for their support and encouragement.

- Telkom South Africa Ltd, TFMC Pty Ltd, M-TEC and THRIP for the financial assistance towards the research projects.

- My whole family for always being there for me.

# **Dedication**

This project is dedicated to my whole family which has always been my pillar of strength.

#### **Abstract**

The global trends towards energy efficiency have facilitated the need for technological advancements in the design and control of power electronic converters for energy processing. The proposed design is intended to make the practical implementation of converters easier.

The development of a universal bidirectional galvanic isolated switch module will be used to drive any MOSFET or IGBT in any position in any topology whether the load is AC or DC. Semiconductor switches are required and are also integrated for fast switching times in power converter applications.

The structure of the power switch module consists of an opto-coupler which will provide an isolation barrier for maximum galvanic isolation between the control circuitry and power stage. It also consists of a high performance gate drive circuit for high speed switching applications with a floating supply.

# **Table of Contents**

| Decla           | ration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ii   |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--|

| Ackno           | owledgements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | iii  |  |

| Dedic           | ation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | iv   |  |

| Abstr           | Dedication Abstract List of Figures List of Tables List of Annexures Glossary of abbreviations and symbols Definition of terms  Chapter 1 Introduction  1 Background 2 Problem statement 3 Objectives of the research 4 Research outcomes 5 Research methodology                                                                                                                                                                                                                                                                              | v    |  |

| List of Figures |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |  |

| List o          | List of Annexures Glossary of abbreviations and symbols Definition of terms  Chapter 1 Introduction  1.1 Background 1.2 Problem statement 1.3 Objectives of the research 1.4 Research outcomes 1.5 Research methodology 1.6 Delimitations 1.7 Value of the research 1.8 Overview of the report 1.9 Summary  Chapter 2 Theoretical considerations  2.1 Introduction 2.2 Power processing 2.2.1 Interdisciplinary nature of power electronics 2.2.2 The need for switching in power electronic circuits 2.3 Comparison of controllable switches | xiii |  |

| List o          | f Annexures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | xiv  |  |

| Gloss           | ary of abbreviations and symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | XV   |  |

| Defin           | ition of terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | xvi  |  |

| Chap            | ter 1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1    |  |

| 1.1             | Background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1    |  |

| 1.2             | Problem statement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3    |  |

| 1.3             | Objectives of the research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4    |  |

| 1.4             | Research outcomes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4    |  |

| 1.5             | Research methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4    |  |

| 1.6             | Delimitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5    |  |

| 1.7             | Value of the research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5    |  |

| 1.8             | Overview of the report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5    |  |

| 1.9             | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7    |  |

| Chap            | ter 2 Theoretical considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8    |  |

| 2.1             | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8    |  |

| 2.2             | Power processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 10   |  |

| 2.2.1           | Interdisciplinary nature of power electronics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11   |  |

| 2.2.2           | The need for switching in power electronic circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 12   |  |

| 2.3             | Comparison of controllable switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 15   |  |

| 2.4             | Power modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17   |  |

| 241             | Structure of the hidirectional switch power module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18   |  |

| 2.4.2  | Operation of the switch module                                    | 19 |

|--------|-------------------------------------------------------------------|----|

| 2.4.3  | Bidirectional switches                                            | 20 |

| 2.5    | Power semiconductor devices                                       | 21 |

| 2.5.1  | Voltage-controlled devices                                        | 22 |

| 2.6    | Theoretical overview of MOSFETs                                   | 23 |

| 2.6.1  | Safe operation area (SOA)                                         | 26 |

| 2.6.2  | Gate voltage limitations                                          | 28 |

| 2.7    | Ground referenced gate drive with PWM direct drive                | 31 |

| 2.8    | Gate drive requirements                                           | 31 |

| 2.8.1  | The impedance of the gate circuit                                 | 32 |

| 2.8.2  | Design consideration of the gate resistor                         | 35 |

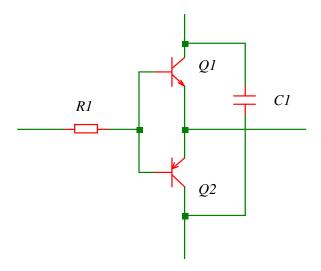

| 2.8.3  | Bipolar totem-pole drive circuit                                  | 36 |

| 2.9    | Gate drive techniques and ICs                                     | 37 |

| 2.10   | Floating supply                                                   | 41 |

| 2.10.1 | Level shifting                                                    | 42 |

| 2.10.2 | Selection of frequency                                            | 44 |

| 2.11   | Power converters                                                  | 45 |

| 2.11.1 | Magnetic components and circuit design                            | 46 |

| 2.11.2 | Skin effect and proximity in effect a conductor wire              | 46 |

| 2.12   | DC-DC switch-mode converters                                      | 49 |

| 2.12   | Non-isolated DC-DC converters                                     | 49 |

| 2.12.1 | Buck converter                                                    | 49 |

| 2.12.2 | Isolated DC-DC converter topology                                 | 52 |

| 2.12.3 | Half-bridge converter                                             | 52 |

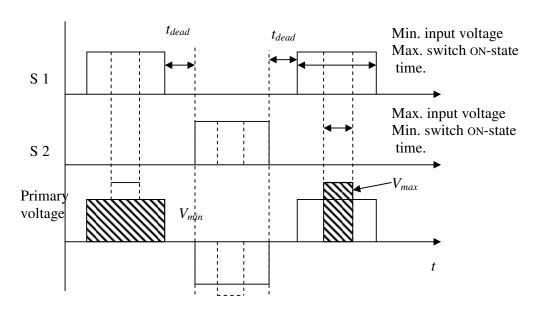

| 2.12.4 | Interlock delay time minimization for half-bridge DC-DC converter | 53 |

| 2.13   | Single-phase AC voltage controller with ON/OFF control            | 57 |

| 2.14   | Heat dissipation                                                  | 60 |

| 2.15   | Summary                                                           | 61 |

|        |                                                                   |    |

| Chapt  | er 3 Design aspects of the switch module                          | 62 |

|        |                                                                   |    |

| 3.1    | Introduction                                                      | 62 |

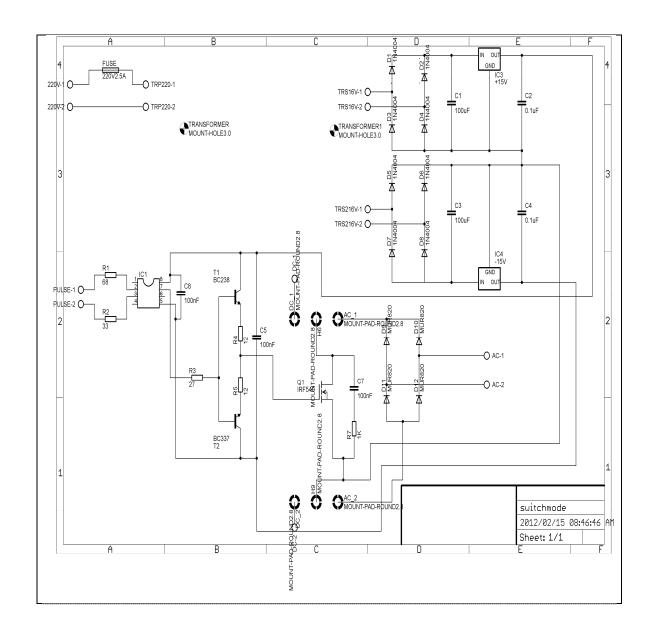

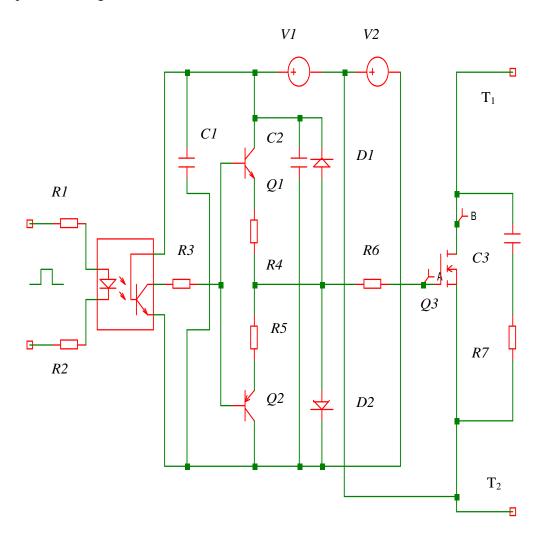

| 3.2   | A detailed circuitry of the bidirectional switch module          | 62  |

|-------|------------------------------------------------------------------|-----|

| 3.2.1 | Isolated power supply                                            | 64  |

| 3.2.2 | Opto-coupler circuit                                             | 66  |

| 3.2.3 | Gate-drive circuit                                               | 66  |

| 3.2.4 | Driver protection                                                | 66  |

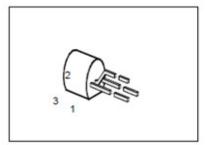

| 3.3   | Choice of switches                                               | 67  |

| 3.3.1 | Snubber circuit                                                  | 67  |

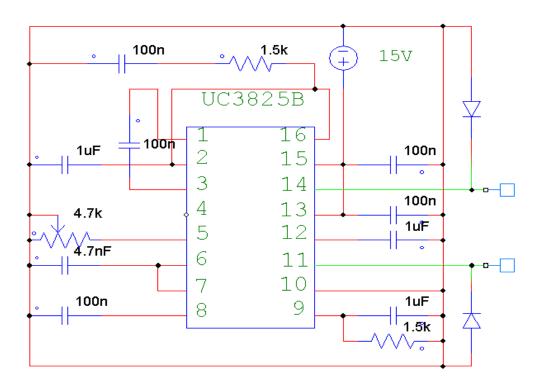

| 3.4   | Test control circuit                                             | 68  |

| 3.4 1 | Test control simulation results                                  | 69  |

| 3.5   | Simulating the gate drive circuit                                | 70  |

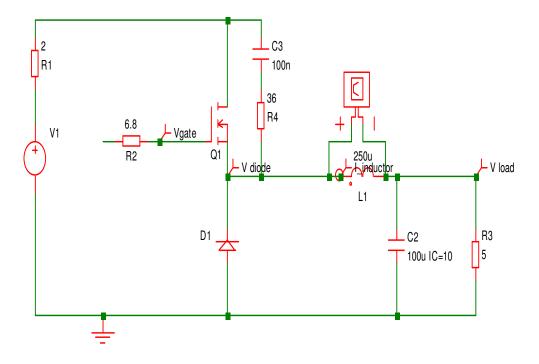

| 3.6   | Design of DC-DC buck converter                                   | 73  |

| 3.6.1 | Buck converter simulations                                       | 75  |

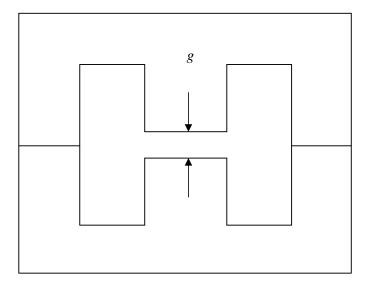

| 3.6.2 | Inductor design                                                  | 78  |

| 3.7   | Design of a half-bridge converter                                | 80  |

| 3.7.1 | Half-bridge mathematical calculations                            | 82  |

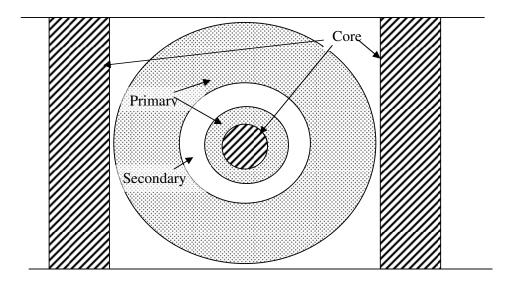

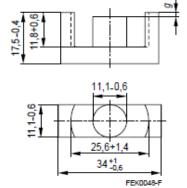

| 3.7.2 | High-frequency transformer design                                | 83  |

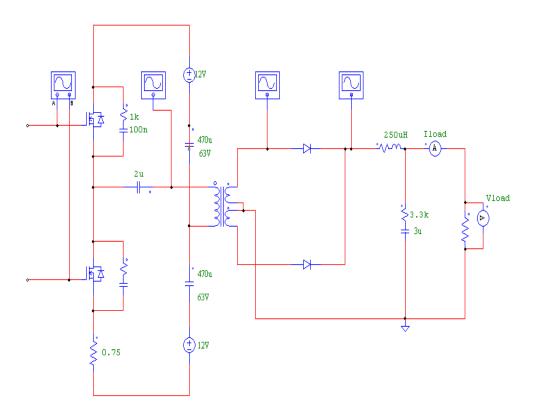

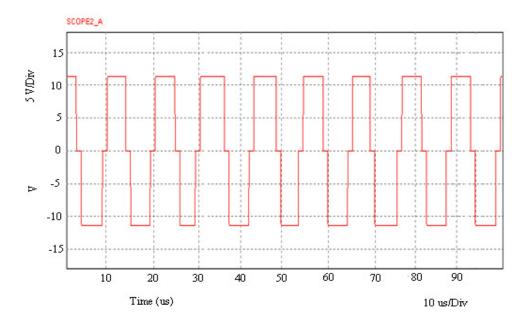

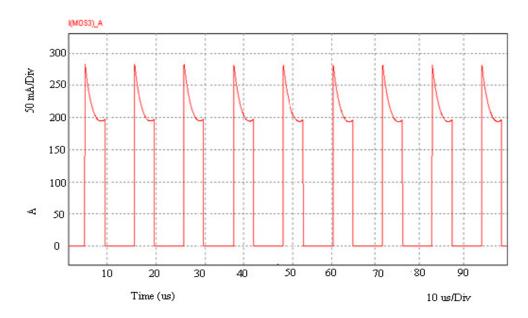

| 3.7.3 | High-bridge converter simulations                                | 84  |

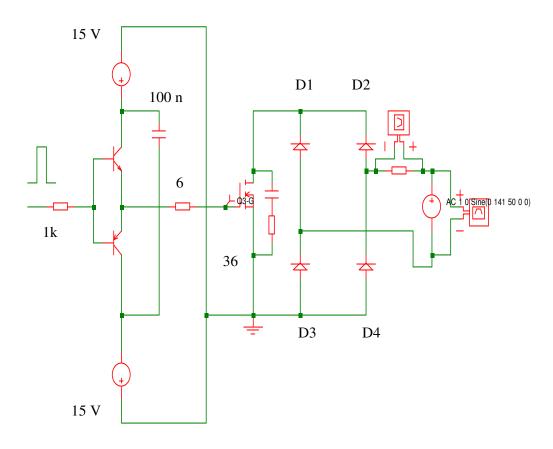

| 3.8   | AC chopper with UC3825N as the controller                        | 86  |

| 3.8.1 | Mathematical calculation of the output voltage                   | 86  |

| 3.8.2 | AC converter simulation graphs                                   | 87  |

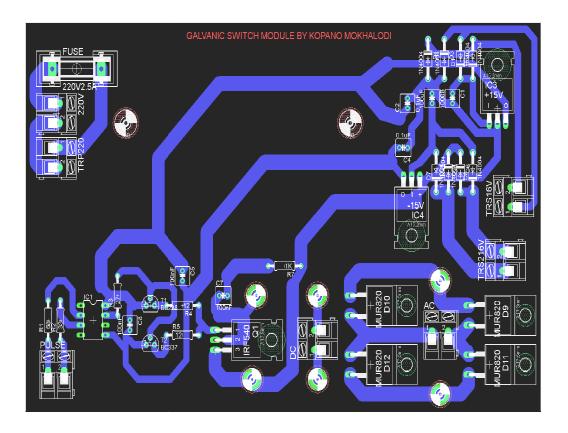

| 3.9   | PCB board manufacturing and tracks                               | 90  |

| 3.10  | Completed prototype module                                       | 91  |

| 3.11  | Summary                                                          | 92  |

| Chap  | ter 4 Measurements and results                                   | 93  |

| 4.1   | Introduction                                                     | 93  |

| 4.2   | Electrical characteristics of the power switch module            | 93  |

| 4.3   | Application example of the switch module to converter topologies | 97  |

| 4.3.1 | Buck converter                                                   | 97  |

| 4.4.2 | Bridge converter                                                 | 99  |

| 4.5.1 | AC converter                                                     | 103 |

| 4.6 Summary |                                       | 106 |

|-------------|---------------------------------------|-----|

| Chap        | ter 5 Conclusions and recommendations | 108 |

| 5.1         | Introduction                          | 108 |

| 5.2         | Conclusions                           | 108 |

| 5.3         | Recommendations                       | 109 |

| Refer       | rences                                | 110 |

| ANNI        | EXURES                                | 119 |

# **List of Figures**

| Figure 1:  | Block diagram of a power electronic system                        | 10 |

|------------|-------------------------------------------------------------------|----|

| Figure 2:  | Interdisciplinary nature of power electronics                     | 12 |

| Figure 3:  | Switching and output waveforms                                    | 14 |

| Figure 4:  | Device operating regions: voltage vs frequency                    | 15 |

| Figure 5:  | Device operating regions: current vs frequency                    | 16 |

| Figure 6:  | Generalized power converter system                                | 17 |

| Figure 7:  | Power switch module shown in block diagram                        | 19 |

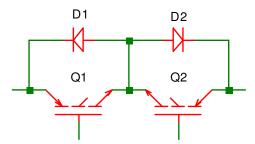

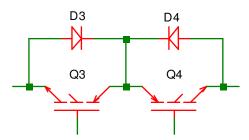

| Figure 8:  | Bidirectional switches in common-emitter configuration            | 20 |

| Figure 9:  | Bidirectional switches in common-collector configuration          | 21 |

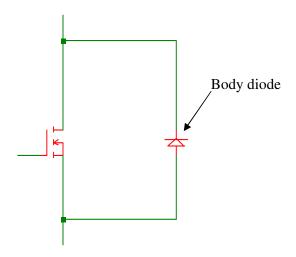

| Figure 10: | MOSFET internal body diode                                        | 24 |

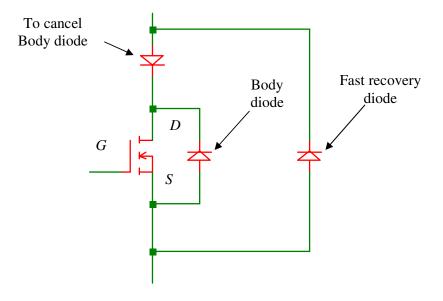

| Figure 11: | Implementation of a fast recovery body diode                      | 24 |

| Figure 12: | Equivalent MOSFET representation junction capacitances            | 25 |

| Figure 13: | A typical graph for Safe operation areas (SOA) for MOSFET         | 26 |

| Figure 14: | On-state resistance against temperature                           | 27 |

| Figure 15: | Bipolar totem-pole MOSFET driver                                  | 31 |

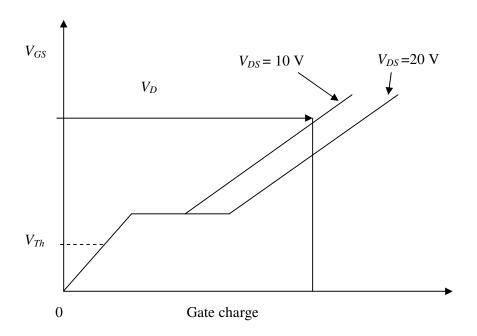

| Figure 16: | Typical gate charge to gate-to-source voltage                     | 34 |

| Figure 17: | Bipolar totem-pole drive circuit                                  | 37 |

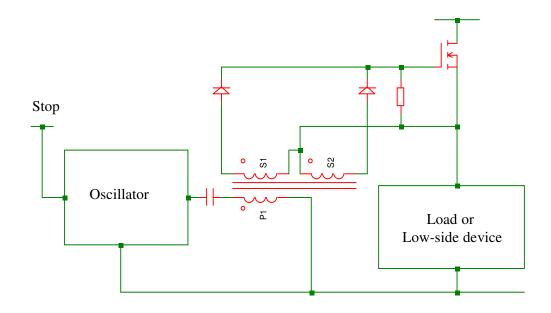

| Figure 18: | Block diagram of a carrier gate-drive technique                   | 38 |

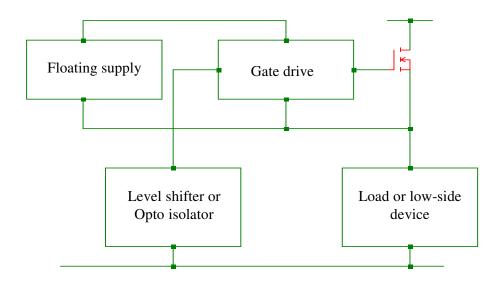

| Figure 19: | Basic block diagram of a floating supply gate-drive technique     | 38 |

| Figure 20: | Basic block diagram of a bootstrap capacitor gate-drive technique | 39 |

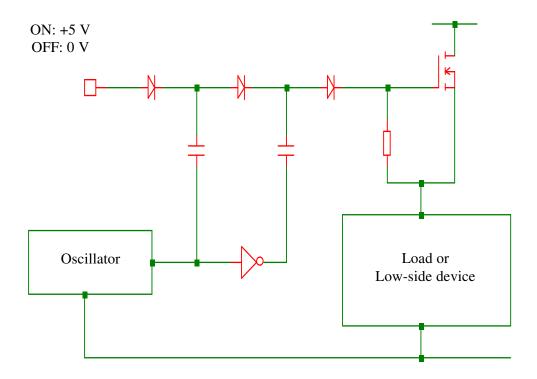

| Figure 21: | Basic block diagram of a charge pump gate-drive technique         | 40 |

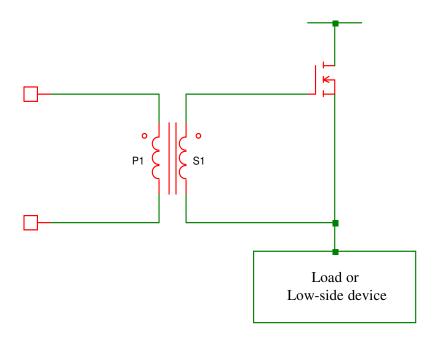

| Figure 22: | Basic block diagram of a pulse transformer gate-drive technique   | 41 |

| Figure 23: | The concept of level shifting                                     | 42 |

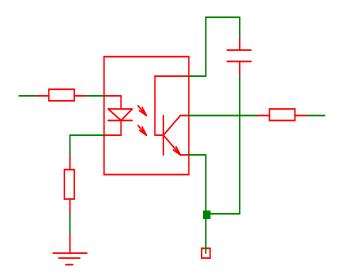

| Figure 24: | Schematic diagram containing an opto-coupling circuit             | 44 |

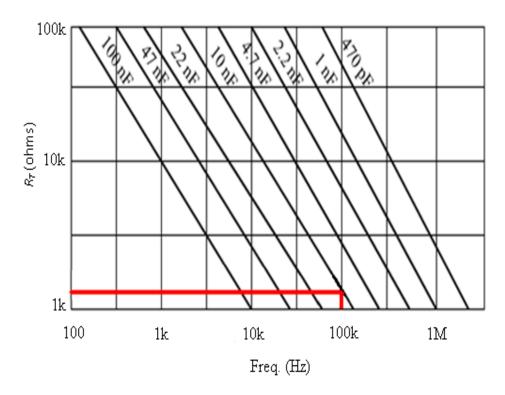

| Figure 25: | A simple $C_T R_T$ nomograph                                      | 45 |

| Figure 26: | Types of eddy-current effects in Litz wire                        | 48 |

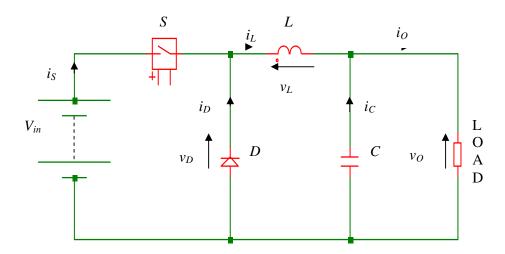

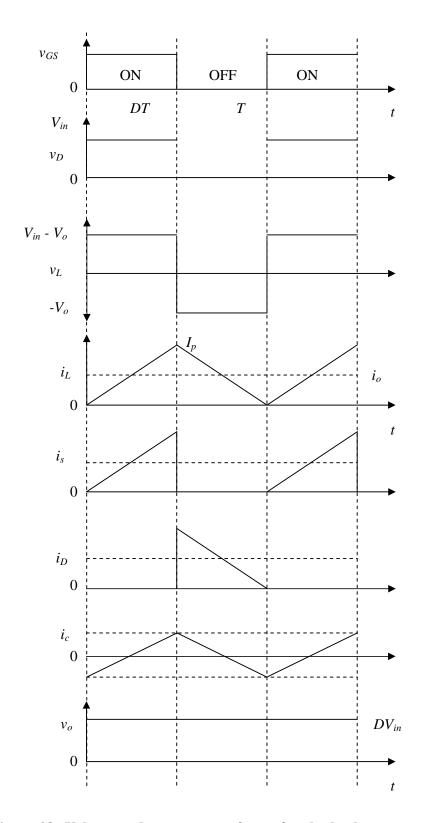

| Figure 27: | Circuit diagram of the buck converter                             | 49 |

| Figure 28: | Voltage and current waveforms for the buck converter              | 51 |

| Figure 29: | Basic half-bridge converter topology                              | 53 |

| Figure 30: | Timing diagrams of a half-bridge converter                                | 54 |

|------------|---------------------------------------------------------------------------|----|

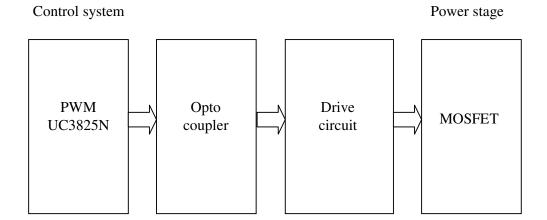

| Figure 31: | Control signal flow in the experimental converter                         | 55 |

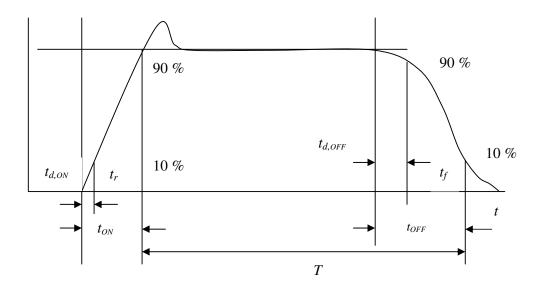

| Figure 32: | Switching transients of a typical MOSFET                                  | 55 |

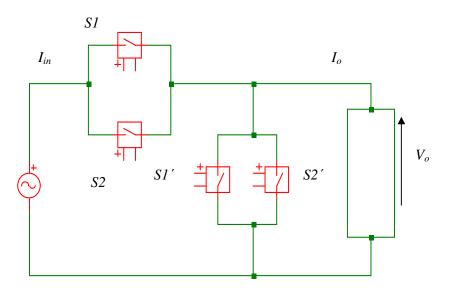

| Figure 33: | Circuit diagram of an AC regulator                                        | 57 |

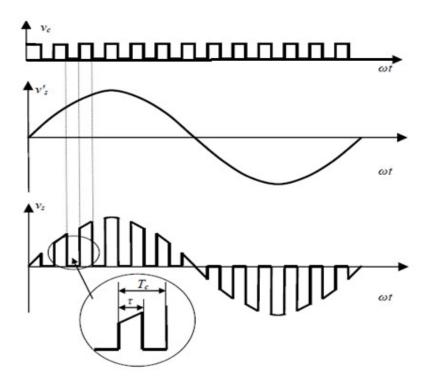

| Figure 34: | Output waveform in AC choppers                                            | 59 |

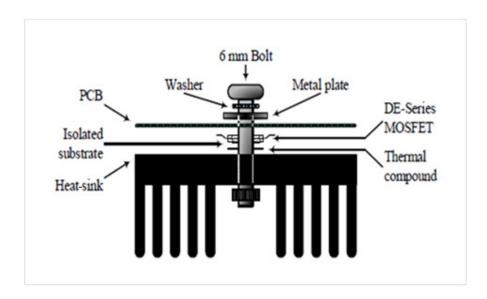

| Figure 35: | Mounting a MOSFET on a heat sinks                                         | 60 |

| Figure 36: | A detailed circuitry of the bidirectional switch module                   | 63 |

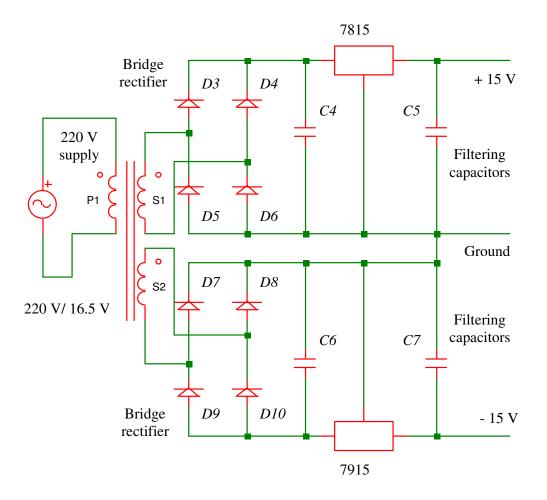

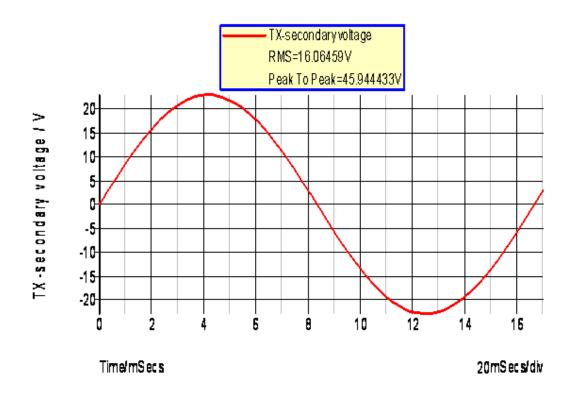

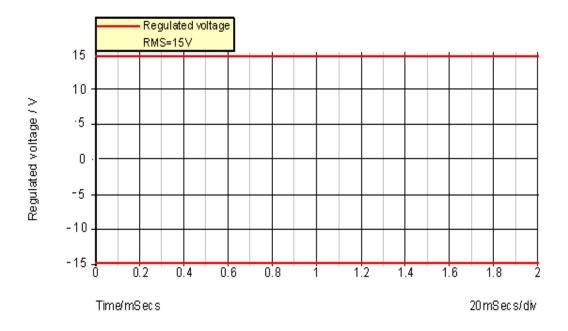

| Figure 37: | Isolated power supply for a gate drive circuit                            | 64 |

| Figure 38: | Transformed $V_{AC}$ supply                                               | 65 |

| Figure 39: | Regulated dual supply 15-0-15 V                                           | 65 |

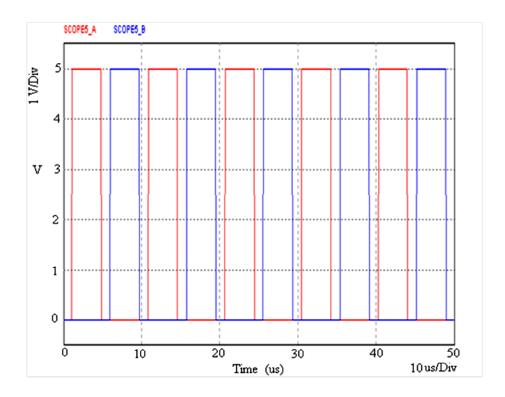

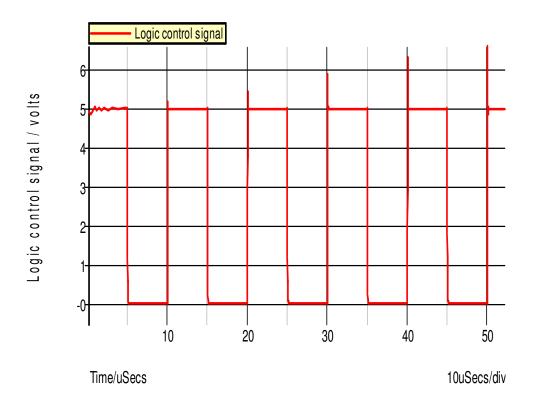

| Figure 40: | Simulation model for control circuit                                      | 68 |

| Figure 41: | PSIM Simulation results of control with dead time                         | 69 |

| Figure 42: | SIMetrix simulations results of a control model                           | 70 |

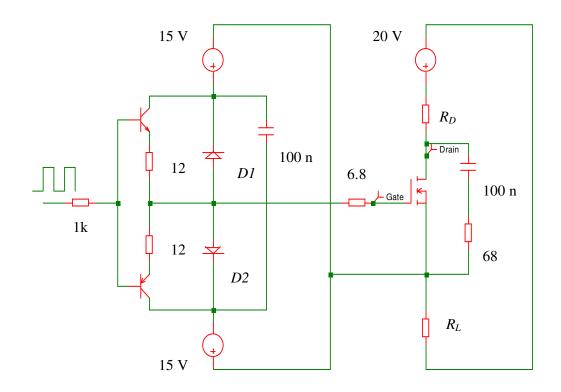

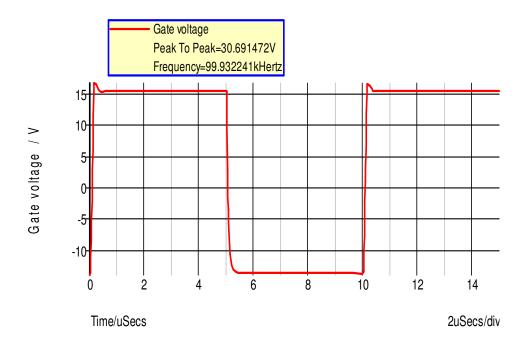

| Figure 43: | Simulation model of the complementary totem-pole drive                    | 71 |

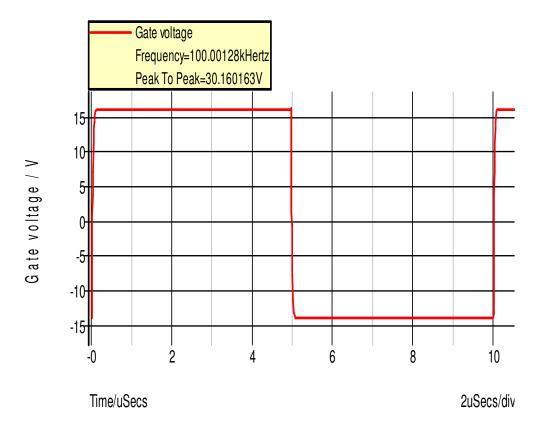

| Figure 44: | Gate-to-source voltage swing between + $15 \text{ V}$ and $-15 \text{ V}$ | 71 |

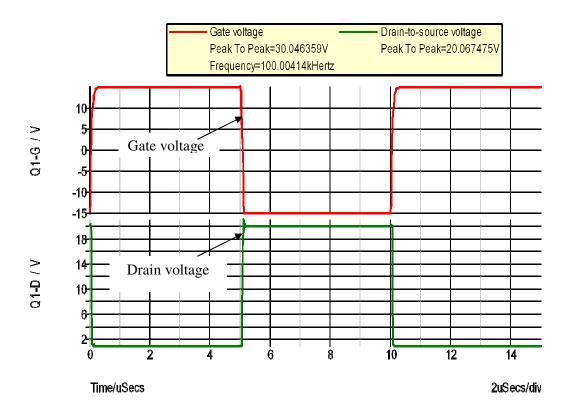

| Figure 45: | Gate voltage and drain output voltage                                     | 72 |

| Figure 46: | Simulation model of a buck converter                                      | 74 |

| Figure 47: | Gate voltage into the MOSFET                                              | 75 |

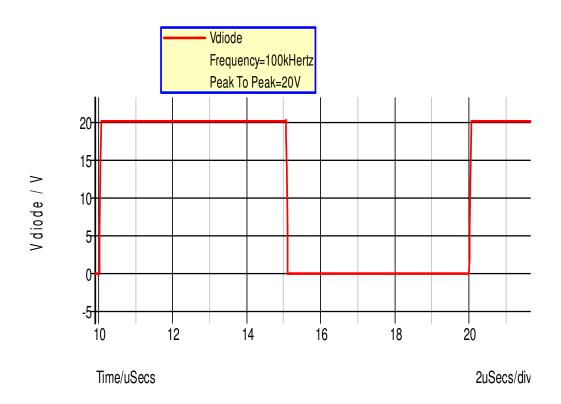

| Figure 48: | Diode voltage in a buck converter                                         | 76 |

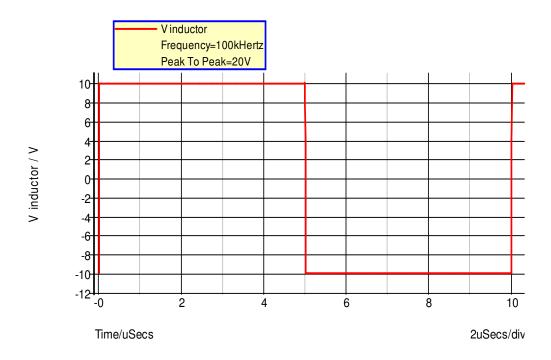

| Figure 49: | Inductor voltage in a buck converter                                      | 76 |

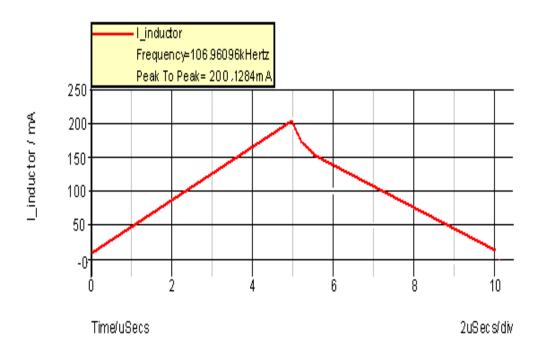

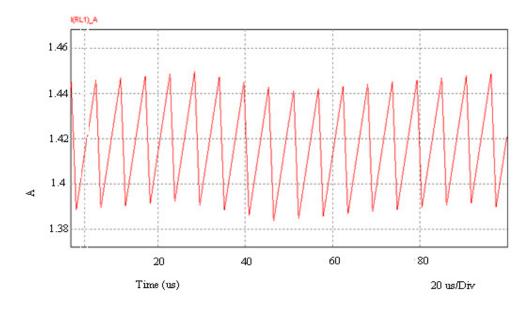

| Figure 50: | Inductor current                                                          | 77 |

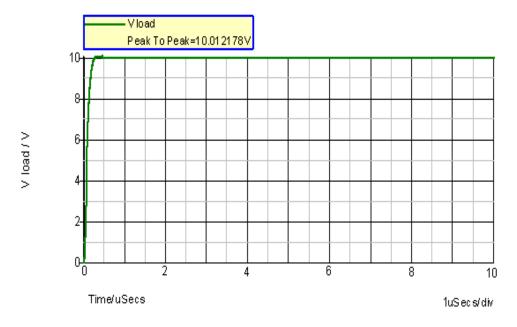

| Figure 51: | Output voltage in a buck converter                                        | 77 |

| Figure 52: | Air gap in an E-core                                                      | 79 |

| Figure 53: | An inductor constructed with Litz wire                                    | 80 |

| Figure 54: | Simulation model of a half-bridge converter                               | 81 |

| Figure 55: | Cross section of a HF transformer                                         | 84 |

| Figure 56: | Voltage measured at the primary of the transformer                        | 84 |

| Figure 57: | Transformer primary current                                               | 84 |

| Figure 58: | Inductor current                                                          | 85 |

| Figure 59: | Rectified voltage                                                         | 86 |

| Figure 60: | Simulation model of the AC chopper system in SIMetrix                     | 87 |

|            |                                                                           |    |

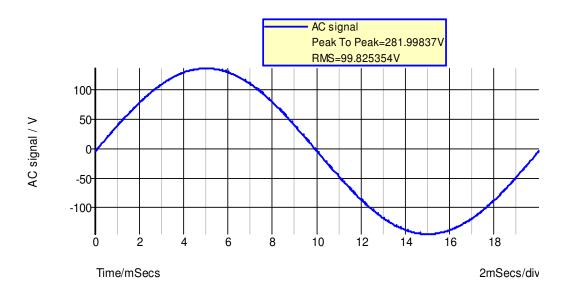

| Figure 61: | AC signal at 100 V/50 Hz                                    | 88  |

|------------|-------------------------------------------------------------|-----|

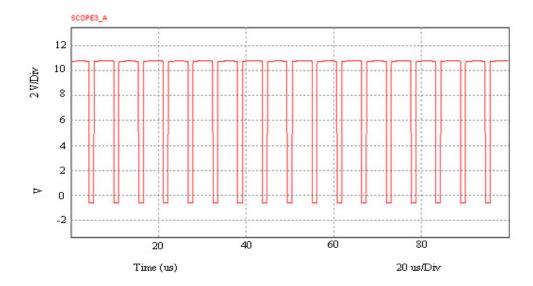

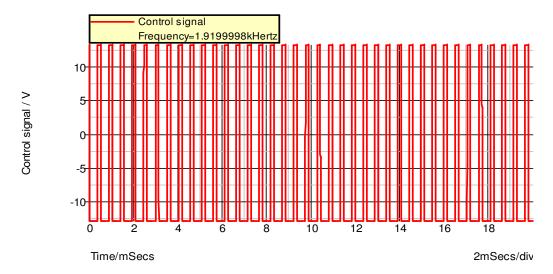

| Figure 62: | Control signal at 1.92 kHz                                  | 88  |

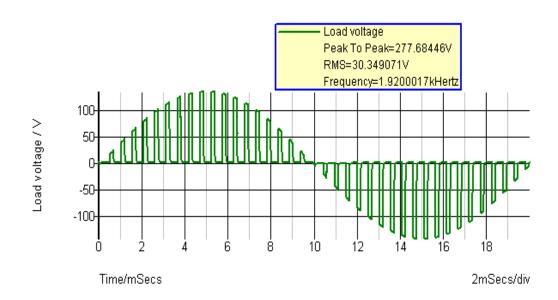

| Figure 63: | Simulation graph for load voltage with 30 % duty cycle      | 89  |

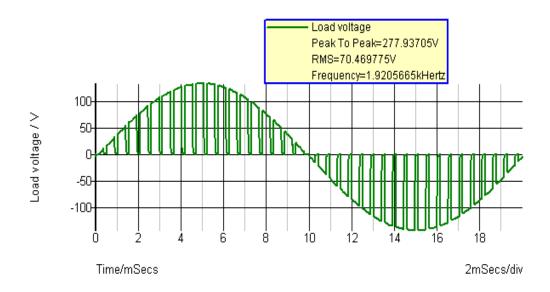

| Figure 64: | Simulation graph for load voltage with 70 % duty cycle      | 89  |

| Figure 65: | PCB board layout of the module in Eagle software            | 90  |

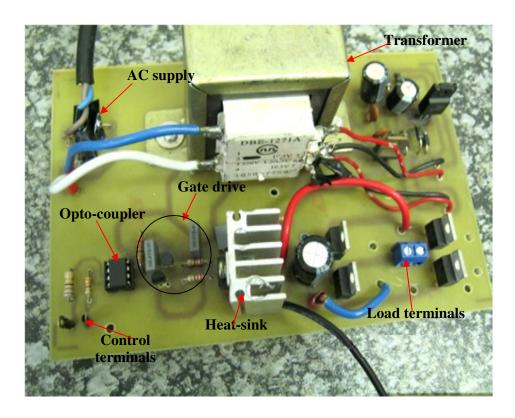

| Figure 66: | Prototype of the switch module                              | 91  |

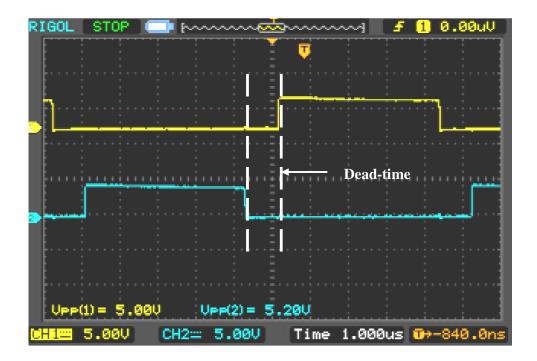

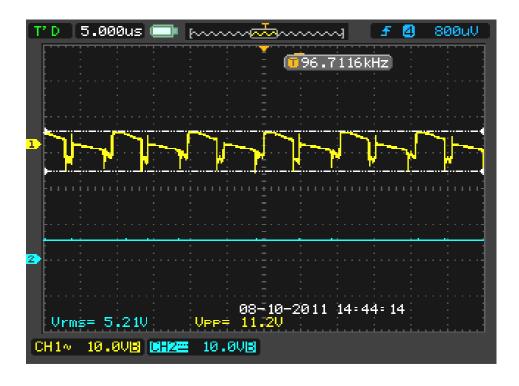

| Figure 67: | Main control signals from the PWM controller                | 94  |

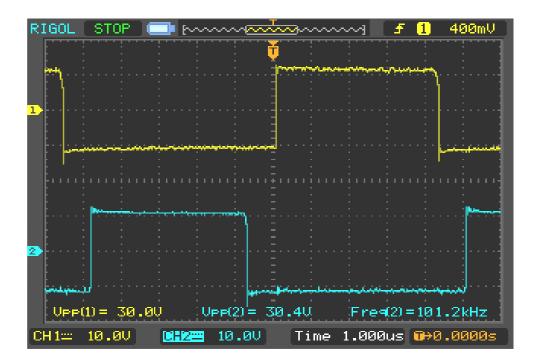

| Figure 68: | Gate voltages $V_{GS}$ of both switches                     | 95  |

| Figure 69: | Characteristic current and voltage waveforms at turn-on     | 96  |

| Figure 70: | Characteristic current and voltage waveforms at turn-OFF    | 96  |

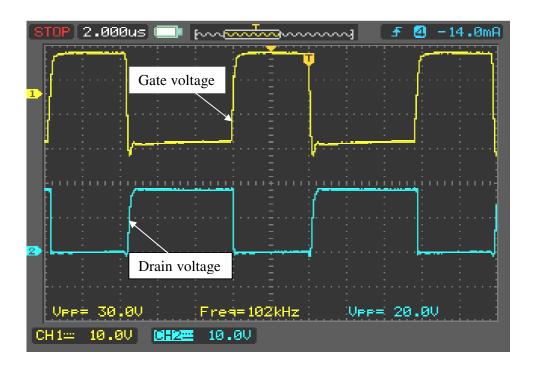

| Figure 71: | The gate voltage and drain output voltage signals           | 97  |

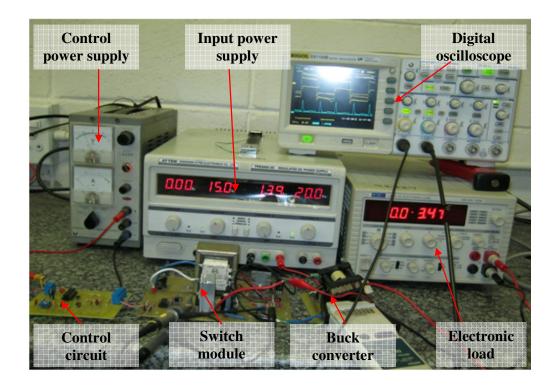

| Figure 72: | Experimental set-up for a buck converter                    | 98  |

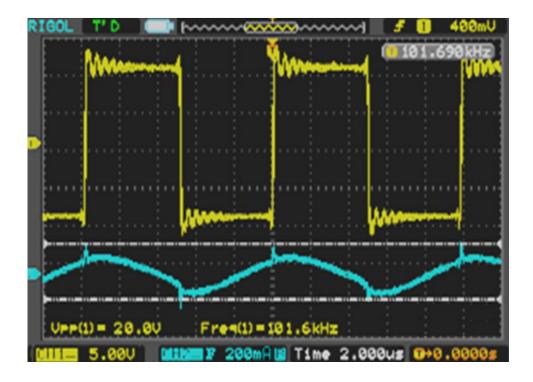

| Figure 73: | Voltage and current waveforms of a buck converter prototype | 99  |

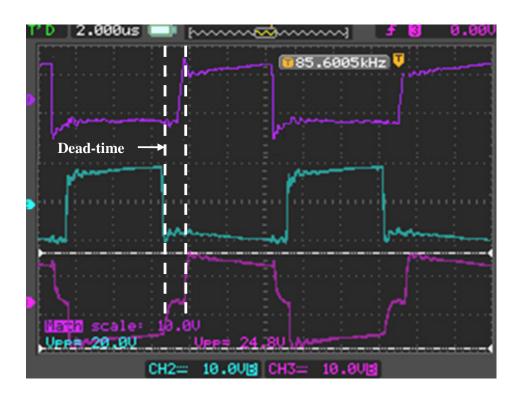

| Figure 74: | Gate voltages of both switches and lower switch voltage     | 100 |

| Figure 75: | Transformer secondary voltage and primary current           | 101 |

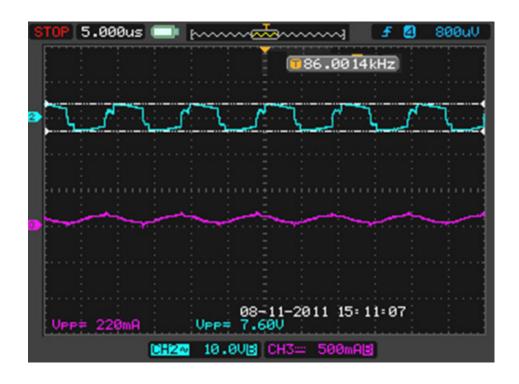

| Figure 76: | Half-bridge secondary voltage and inductor current          | 102 |

| Figure 77: | Half-bridge rectified voltage and output voltage            | 102 |

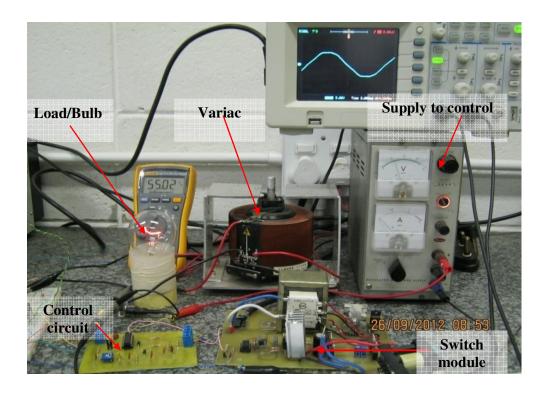

| Figure 78: | Practical set-up for AC converter                           | 103 |

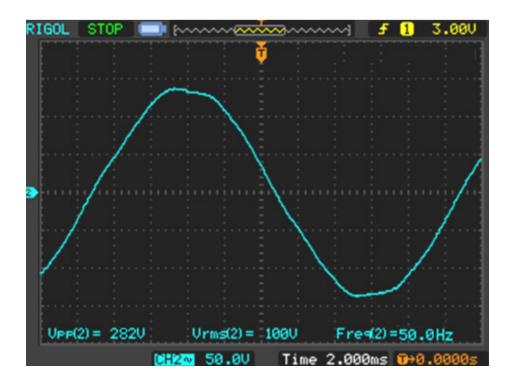

| Figure 79: | AC source adjusted to 100 V/50 Hz                           | 104 |

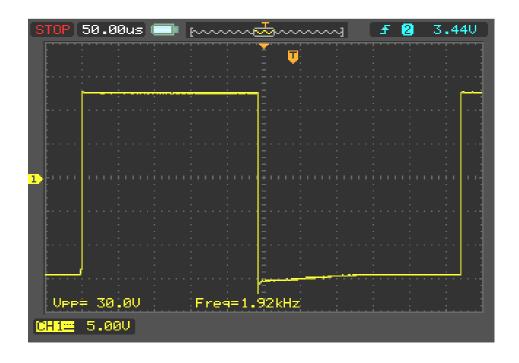

| Figure 80: | Control signal at 1.92 kHz                                  | 105 |

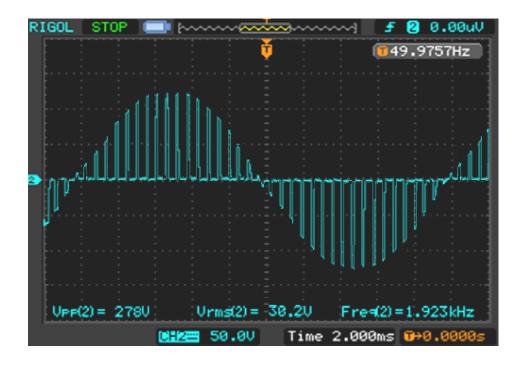

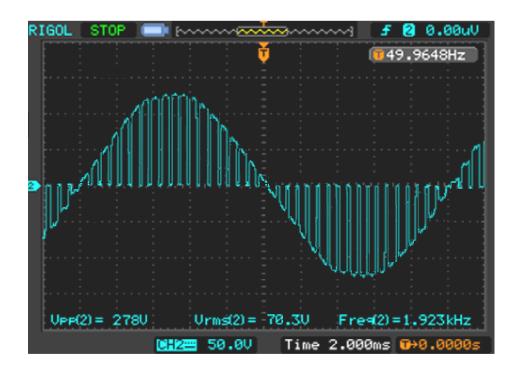

| Figure 81: | Load voltage at 30 % duty cycle                             | 105 |

| Figure 82: | Load voltage at 70 % duty cycle                             | 106 |

# **List of Tables**

| Table 1: | Relative properties of controllable switches       | 15 |

|----------|----------------------------------------------------|----|

| Table 2: | Buck converter specifications                      | 73 |

| Table 3: | Half-bridge converter specifications               | 81 |

| Table 4: | Calculated output results for different duty ratio | 86 |

# **List of Annexures**

| Annexure A: | MOSFET IRF 530N datasheet                     | 119 |

|-------------|-----------------------------------------------|-----|

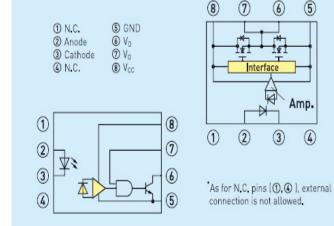

| Annexure B: | Opto-coupler PC925L datasheet                 | 120 |

| Annexure C: | PWM UC3825N datasheet                         | 121 |

| Annexure D: | BC327 BJT datasheet                           | 123 |

| Annexure E: | BC337 BJT datasheet                           | 124 |

| Annexure F: | ETD/34/N87 core                               | 126 |

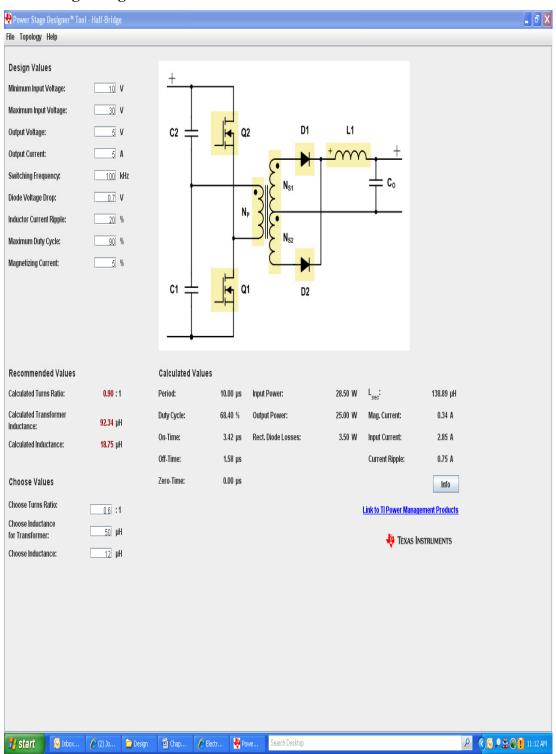

| Annexure G: | Power Stage designer tool                     | 127 |

| Annexure H: | MUR820 Power diodes rectifiers' datasheet     | 128 |

| Annexure I: | Complete circuit diagram of the switch module | 129 |

# Glossary of abbreviations and symbols

| <u>A</u>                                 | mA - Milliamps                                       |

|------------------------------------------|------------------------------------------------------|

| A - Amperes                              | MOSFET - Metal-oxide semiconductor field             |

| AC - Alternating current                 | effect transistor                                    |

| D                                        | N                                                    |

| B                                        | N Essisiana                                          |

| BJT - Bipolar junction transistor        | $\eta$ - Efficiency                                  |

| <u>C</u>                                 | <u>0</u>                                             |

| ° C - Degrees Celsius                    | <u>υ</u><br>Ω - Ohm                                  |

|                                          | SZ - Olilli                                          |

| <u>D</u>                                 | <u>P</u>                                             |

| DC - Direct current                      | PWM - Pulse-width modulation                         |

|                                          |                                                      |

| <u>E</u>                                 | Q                                                    |

| ESR- Equivalent series resistance        | q - Charge of an electron, 1.062 x 10 <sup>-19</sup> |

| EMI - Electromagnetic interference       |                                                      |

|                                          | <u>R</u>                                             |

| <u>F</u>                                 | R - Resistance                                       |

| F - Farad                                |                                                      |

| FC - Fuel cell                           | <u>s</u>                                             |

|                                          | s - Second                                           |

| <u>H</u>                                 |                                                      |

| H - Henry                                | T                                                    |

|                                          | $t_{OFF}$ - OFF-time of a switch                     |

| <u>I</u>                                 | $t_{ON}$ - ON-time of a switch                       |

| $I_O$ - Output current                   |                                                      |

| IGBT – Insulated-gate bipolar transistor | <u>v</u>                                             |

|                                          | V - Volts                                            |

| I                                        | $V_D$ - Voltage across a diode                       |

| J - Joule                                | $V_{DC}$ - Direct current voltage                    |

|                                          | $V_{IN}$ - Input voltage                             |

| <u>K</u>                                 | $V_O$ - Output voltage                               |

| kW - Kilowatts                           |                                                      |

|                                          | <u>W</u>                                             |

| <u>M</u>                                 | W – Watts                                            |

| $\mu$ - Micro, $10^{-6}$                 |                                                      |

|                                          |                                                      |

#### **Definition of terms**

**Algorithm:** An ambiguous description of a finite set of operations for solving a computational problem in a finite amount of time.

**Bidirectional:** Capability to block the voltage and to conduct current in both directions.

**Chopping:** A technique of rapidly switching ON and OFF a source of voltage.

**Fuel cell:** A device that produces electricity through an electrochemical process, usually from hydrogen and oxygen.

**Galvanic isolation:** The principle of isolating functional sections of electrical systems to prevent current flow, no metallic conduction path is permitted.

**Nomograph:** Alignment chart or abaque, which can be used for graphically calculating the resistance or used to estimate resistance or capacitance points at various frequencies.

**Pulse width modulation:** A powerful technique for controlling analog circuits with a microprocessor's digital outputs, employed in a wide variety of applications, ranging from measurement and communications to power control and conversion.

**Renewable energy:** A form of energy which is never exhausted because it is renewed by nature.

**Uninteruptable power supply:** An electrical apparatus that provides emergency power to a load when the input power source typically mains power, fails.

#### **Chapter 1 Introduction**

#### 1.1 Background

It is clear that rapid technology evolution coupled with the population explosion has resulted in an increase in average electrical power use (Kularatna 1998:2). This magnitude of growth increases the global energy demand for electricity and with the limited sources of fossil fuels (oil, gas, coal) which have traditionally provided this energy, depleting, the world has turned to the use of renewable energy as the targeted energy market, example being Fuel Cells (FC) (Archer & Hill 2001:16).

These global trends towards energy efficiency have forced researchers to come up with technological advancements in the design and control of power electronic converters for energy processing (Khan 2007:543). According to Khan (2007:543) these power electronic converters can be used in a variety of applications such as:

• Consumer electronics

Telecommunications equipment, cellular, telephones, cameras charging and computer power supplies,

Automobile industries

Electronic ignitions and lighting,

Commercial sectors

Variable speed motor drives for conveyor belt systems, heating, installations for metals processing, uninterruptible power supplies (UPS) and industrial welding,

Domestic electronics

Fluorescent, compact fluorescent and incandescent lighting, washing machines, cooking appliances, and dishwashers,

Utility applications

DC transmission lines for electrification purposes.

According to (Rashid 2001:xi) all these applications utilise similar power converter

topologies which allow for controlled and efficient power conversion from one form of energy to another, utilising semiconductor technologies such as BJT transistors, SCRs (thyristors), IGBTs and power MOSFETs. Kularatna (1998:2) as quoted by Rashid (2004:1) described these power conversion electronics "as a group of electrical and electronic components arranged to form an electric circuit or group of circuits for the purpose of modifying or controlling electric power from one form to another."

Khan (2007:543) refers to Pirelli Tyres who coined the phrase "Power is nothing without control." Khan (2007:549) also stresses the point that this gate drive circuitry of a power converter should be considered as an important enabling interface between the power electronics and the control stage. It is therefore of utmost importance that researchers and engineers pay much attention in the design of this interface between the control and power electronics, since it can have a substantial impact on the performance and reliability of a power electronic system (Khan 2007:549).

As Kularatna (1998:1) states "the core of most power electronic apparatus consists of a converter using power semiconductor switching devices that work under the guidance of control electronics." From the electrical point of view, these power converters can be classified as rectifiers (AC-DC converters), inverters (DC-AC converters), DC-DC converters or an AC power controllers running at the same frequency (Mohan, Undeland & Robbins 2003:703).

The motivation for using switching devices in a converter is to increase the conversion efficiency to a high value. Power electronics can be described as an area where anything from few watts to over several hundred megawatts order powers are controlled by semiconductor controlled elements (Mohan *et al* 2003:703). These semiconductor devices are close to ideal switching, i.e. they must either be completely ON or completely OFF. In the ON-state the voltage across the switch should ideally be zero, independent of the current. In the OFF-state the opposite must hold true, with zero current independent of the voltage (Grant & Gower 1989:17).

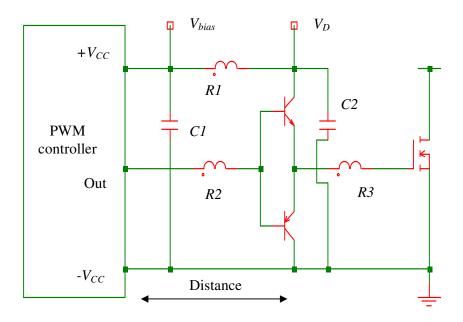

According to Rashid (2004:777) a semiconductor switch is sometimes used where no terminal is connected to the ground potential and it is thus said to be floating. This floating gate drive supply is used to ensure full gate control for indefinite periods of time. A level shifter must also be provided that can sustain full voltage with minimal propagation delays and lower power consumption (Janse van Rensburg 2012:282). The power absorbed by the gate drive circuitry should not significantly affect the overall efficiency (International rectifier 2009). The control circuit supplies a logic signal (0 to 5 V) that indicates when the semiconductor switches must be ON and when they must be OFF. However, most semiconductor switches usually do not accept logic level signals therefore a drive circuit is needed to convert the logic signals to appropriate electrical signal levels (Khan 2007:546).

If the switch is used in a completely different electrical circuit where high voltages and currents are the norm, these high voltage levels may be disastrous to the control circuit and therefore there must be galvanic isolation between the control circuit and the power circuit. This electrical isolation between the control and the drive circuits can be provided by making use of an opto-coupler (Mohan *et al.* 2003:703). Also when switches are used in circuits where they are complementary they may not be ON simultaneously or else they will be destroyed (Mohan *et al.* 2003:706).

#### 1.2 Problem statement

Researchers and designers of solid state power converters all encounter the same problem, i.e. the gate drive circuitry between the control circuit and each semiconductor power device has to be custom designed for the application and the position of the device in the topology. This leads to many hours being spent on optimizing a gate drive for the specific device instead of solving the control algorithms required.

#### 1.3 Objectives of the research

The main objective of this research is the development of a universal bidirectional

galvanic isolated switch module which can be used to drive any MOSFET or IGBT in any position in any topology whether the load is AC or DC. This switch module will be used as an interface between the control circuitry and the conversion topology to solve the interface problems. It will provide a galvanic isolated power source for the gate drive circuitry with sufficient drive power for the MOSFETs or IGBTs.

#### 1.4 Research outcomes

The research is expected to deliver a suitable switch module that can be used in any AC or DC converter circuit with no interface problems between it and the control.

A poster presentation was presented at the SATNAC 2010 conference in Cape Town.

An article will also be submitted to an accredited journal.

#### 1.5 Research methodology

The research commenced with acquisition and study of literature related to the fundamentals of semiconductor switches and their switching speeds. This information, all obtainable from previous scholarly research work, formed a basis for an in-depth analysis of both theoretical and practical concepts on the design of a switch module. The key element in the process was the evaluation of different gate drive techniques, switching devices and level shifting circuits.

A universal bidirectional isolated switch module for power converters was then constructed. Experiments were performed to establish the electrical characteristics of the switch module. The switch was then evaluated in an AC control application as well as in DC applications. Compilation of the research documentation and the dissertation constituted the final phase of the research.

#### 1.6 Delimitations

Design and development of a universal bidirectional galvanic isolated switch module for power converter applications focused only on MOSFETs and IGBTs and their gate drive circuits since both are voltage-controlled devices.

Gate drive for current controlled devices like BJTs is not dealt with in this regard because it is outside the scope of this research.

#### 1.7 Value of the research

Researchers in the fuel cell laboratory at VUT will be able to use the proposed circuit module to implement control algorithms in experimental set-ups without having any interface problems between the control circuit and the conversion topology.

This will shorten the research time by enabling the researchers to focus on their own objectives and not on peripheral issues. This should lead to more research output in a shorter time.

#### 1.8 Overview of the report

This research report consists of five chapters relating to the design and development of the switch module.

Chapter 1 entails an introduction, the background and study of power electronics, the need for the research, as well as the aims and values of the research. The methodology of the research is outlined and the delimitations are presented. It also states the importance of it for other researchers at the institution.

Chapter 2 starts with the introduction and discussion on the history of power electronics. This is followed by the discussion on power processing and the need for switching power electronics circuits. This chapter is devoted to the literature related

to the development of the universal bidirectional galvanic isolated power switch module for power converter applications. It also contains a brief review on power MOSFETs and their characteristics. The drive circuits and techniques currently employed to successfully drive the high-frequency high power MOSFETs are also discussed.

Level-shifting circuits are also addressed. The final complementary totem-pole gate drive circuit is also discussed. This chapter also discusses the control circuitry and the converter topologies that will validate the application of this module.

Chapter 3 deals with the actual design of the switch module and certain converter topologies. The design parameters of the switch and converter are dealt with mathematically and systematically. Computer simulation results are presented, confirming the theoretical predictions that the proposed system can work as predicted.

Chapter 4 is devoted to the explanation of the whole set-up of the experiment. All the experimental work, analysis and measurements performed on the switch module and components are presented. The interaction between the various components and the stages are explained.

In Chapter 5, conclusions and recommendations are drawn, suggestions for further improvements are also presented and hence recommendations are made regarding the design.

#### 1.9 Summary

This chapter presented the underlying factors and reasons that necessitated the undertaking of the research as well as its importance and relevance. The background and research methodology used in the research has been provided as well as an overview of the dissertation.

The theoretical study of power electronics components, their characteristics, operation and application are discussed in the next chapter.

#### Chapter 2 Theoretical considerations

The previous chapter covered the background, the problem statement and the primary objectives of this study as well as the need for this research. The methodology of the research study, the delimitations and approach were presented as well as the value the research has for the institution as a whole.

This chapter is devoted to the literature related to the development of the universal bidirectional galvanic isolated power switch module for power converter applications. Relative properties of controllable switches were compared and contrasted. Drive circuits techniques and requirements were also discussed and compared. Lastly the components that make up the module were also discussed together with the converter topologies that validate it.

#### 2.1 Introduction

The history of power electronics began with the introduction of the mercury-arc rectifier in 1900 (Rashid 2004:2). Then, the metal tank rectifier, grid-controlled vacuum-tube rectifier, ignitron, phanotron and thyratron were introduced gradually and were applied for power control until the 1950s (Moorthi 2005:1).

Rashid (2001:ix) further states that the first electronics revolution began in 1948 with the invention of the silicon transistor by Bardeen, Bratain and Schockley at Bell Telephone Laboratories. Most of today's advanced electronic technologies are traceable to that invention and modern micro-electronics evolved over the years from these silicon semiconductors (Rashid 2001:xi).

According to Moorthi (2005:1) the second electronics revolution began with the development of a commercial thyristor by the General Electric Company in 1958. That was the beginning of a new era of power electronics. Since then, many

different types of power semiconductor devices and conversion techniques have been introduced (Rashid 2001:xi).

The demand for energy, particularly in electrical form, is ever-increasing in order to improve the standard of living (Rashid 2001:xi). Power electronics helps with the efficient use of electricity, thereby reducing power consumption. Semiconductor devices used as switches for power conversion or processing are solid state electronic devices employed for the efficient control of the amount of power and energy flow. Higher efficiency and lower losses are sought for devices for a range of applications, from microwave ovens to high-voltage DC transmission. New devices and power electronic systems have evolved for even more effective control of power and energy (Rashid 2001:xi).

As Rashid (2001:xi) states: "power electronics has already found an important place in modern technology and has revolutionised control of power and energy. And as the voltage and current ratings and switching characteristics of power semiconductor devices keep improving, the range of applications continues to expand in areas such as lamp controls, power supplies to motion control, factory automation, transportation, energy storage, multi-megawatt industrial drives and electric power transmission and distribution."

Rashid (2004:2) further describes that the greater efficiency and higher control features of power electronics are becoming attractive for application in motion control by replacing the earlier electro-mechanical and electronic systems. Application in power transmission includes high voltage DC [HVDC] conversion stations, flexible AC transmission system [FACTS] and static-var control (Mohan *et al.* 2003:8). In power distribution these include DC-AC conversion, dynamic filters, frequency conversion and custom power systems (Moorthi 2005:2).

According to Moorthi (2005:2) it is important to note that all the devices employed for power electronic applications are used in the 'switch' mode. The moments of switching ON or OFF are controlled to fulfill the requirements of the circuit under

consideration. In broad terms, the task of power electronics is to process and control the flow of electric energy by supplying voltages and currents in a form that are optimally suited for user loads (Mohan *et al.* 2003:8-9).

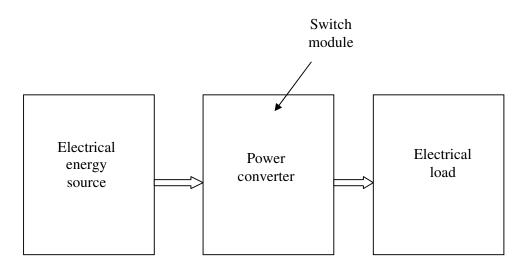

#### 2.2 Power processing

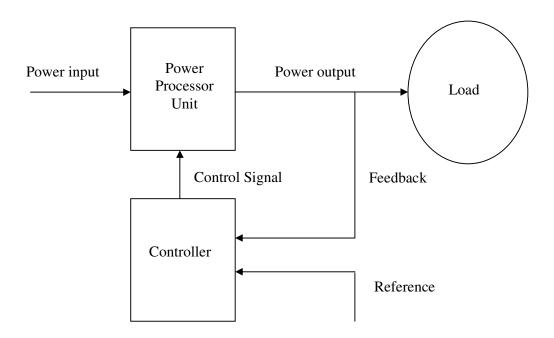

Considering the nature of flow of the electric energy which will suit the load, Mohan *et al.* (2003:3) suggested a model shown in Figure 1 that describes the process and control of electric energy. This model shows a power electronic system in a block diagram form.

Figure 1: Block diagram of a power electronic system (Mohan et al. 2003:3)

According to Erickson & Maksimovic (2001:1) the power input is usually (but not always) from the electric utility at a certain frequency, being single or three-phase. The phase angle between the input voltage and the current depends on the topology and the control of the power processor. The processed output (voltage, current, frequency and the number of phases) is as desired by the load (Mohan *et al.* 2003:3).

If the power processor's output can be regarded as a voltage source, the output current and the phase angle relationship between the output voltage and the current depend on the load characteristic (Mohan *et al.* 2003:3). The feedback controller compares the output of the power processor unit with a desired (or a reference) value and adjust to the required value and by so doing the error between the two is minimized by the controller (Prodic, Maksimovic & Erickson 2001:893). The power flow through such systems may be reversible, thus interchanging the roles of the input and the output (Mohan *et al.* 2003:3).

The controller in the block diagram of Figure 1 consists of linear integrated circuits or digital signal processors (DSP) (Mohan *et al.* 2003:3). Revolutionary advances in microelectronics have led to the development of such controllers. Moreover, these advances in semiconductor fabrication technology have made it possible to significantly improve the voltage and current handling capabilities and the switching speeds of power semiconductor devices, which make up the power processor unit (Rashid 2004:26).

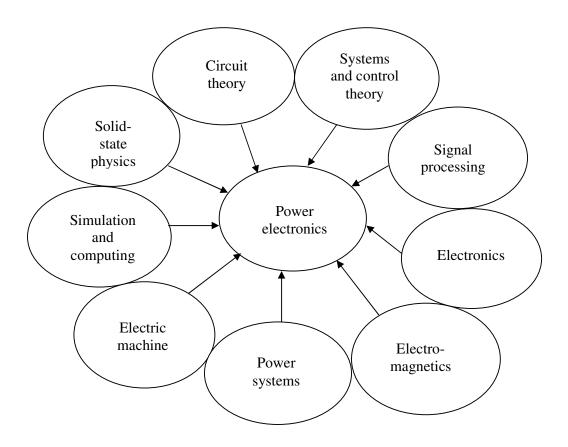

#### 2.2.1 Interdisciplinary nature of power electronics

Mohan *et al.* (2003:14) also came up with a diagram showing the interdisciplinary nature of power electronics which encompasses many fields within electrical engineering as shown in Figure 2. These include power systems, solid-state electronics, electrical machines, analogue and digital control, signal processing, electromagnetic field calculations and so on (Rashid 2001:2).

Combining the knowledge and study of these diverse fields makes the study of power electronics more challenging as well as more interesting (Rashid 2001:2). There are many potential advances in all these fields that can improve the prospects for applying power electronics to new applications (Mohan *et al.* 2003:14). Any useful circuit design for the control of power must address issues of both devices and control as well as of the energy itself. Among the unique aspects of power electronics are its emphasis on large semiconductor devices, the application of

magnetic devices for energy storage and special control methods that must be applied to nonlinear systems (Rashid 2001:2).

Figure 2: Interdisciplinary nature of power electronics (Mohan et al. 2003:14)

#### 2.2.2 The need for switching in power electronic circuits

The need to use semiconductor devices to perform conversion functions is very much related to converter efficiency. In power electronic circuits, the semiconductor devices are generally used as switches, that is, either in the ON-state or the OFF-state (Rashid 2001:76).

This is unlike the case for power amplifiers and linear regulators where semiconductor devices operate in their linear mode and as a result a very large amount of energy is lost within the power circuit before the processed energy reaches the output (Rashid 2001:76). Semiconductor switching devices are used in power electronic circuits because of their ability to control and manipulate very large amounts of power from the input to the output with relatively very low power dissipation in the switching devices. Their use helps to create highly efficient power electronic systems (Rashid 2001:76).

As efficiency is considered an important figure of merit, it does have a significant implication for overall system performance. In low efficiency power systems, large amounts of power are dissipated in the form of heat, which results in one or more of the following (Mohan *et al.* 2003:4):

- Cost of energy increase due to increased consumption,

- Additional design complications might be imposed, especially regarding the design of device heat sinks,

- Additional components such as heat sinks increase the cost, size and weight of the system resulting in a low-power density,

- High-power dissipation, forces the switch to operate at a low switching frequency resulting in a limited band-width, slow response and most importantly, the size and weight of components are large and

- Reduced system reliability.

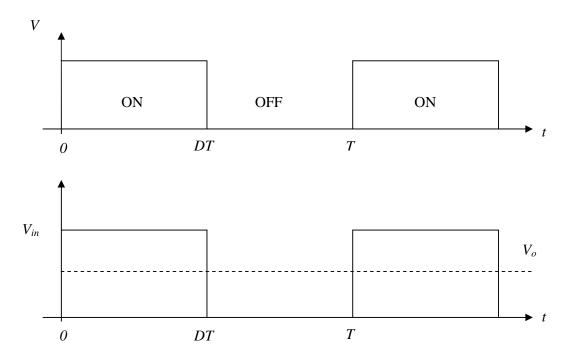

According to Rashid (2001:76) switching by mechanical or electrical means, is the best possible way to achieve high efficiency. However, unlike mechanical switches, electronic switches are more superior by far because of their speed and power-handling capabilities as well as reliability. The advantages of using switches do not come without a cost. Because of the nature of switch currents and voltages (square waveforms), high order harmonics are normally generated in the system. To reduce these harmonics, additional input and output filters are normally added to the system (Baliga 2008:822). According to Rashid (2001:77) if the switch is assumed to be ideal and is periodically turned ON and OFF, then a typical output voltage  $V_o$  waveform can be seen as in Figure 3 and its average value given by:

$$V_o = \frac{1}{T} \int_0^T V_{in} dt = V_{in} D$$

(Volts)

Where:

$D \equiv \text{duty cycle}$   $T \equiv \text{period of the waveform in s}$   $V_{in} \equiv \text{input voltage in V}.$

Moreover, depending on the device type and power electronic circuit topology used, the device driver circuit and the circuit protection (snubbers) can significantly increase both the complexity of the system and its cost (Erickson & Maksimovic 2001:14).

Figure 3: Switching and output waveforms (Rashid 2001:77)

#### 2.3 Comparison of controllable switches

Mohan et al. (2003:29) points out that only a few definite statements can be made in comparing these devices because a number of properties must be considered

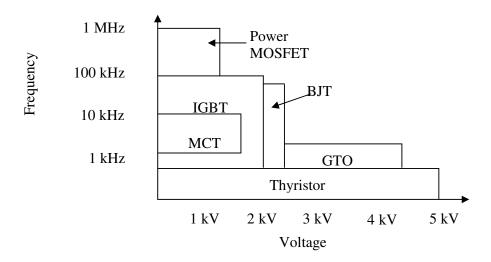

simultaneously and the devices are still evolving at a rapid pace. However, the qualitative observations given in Table 1 can be made. From this table, although the MOSFET has a low power capability when it comes to switching speed it is the fastest (Mohan *et al.* 2003:29). Again, a summary of power devices capabilities is shown in Figure 4 (Rashid 2001:64).

Table 1: Relative properties of controllable switches (Mohan et al. 2003:29)

| Device | Power Capability | Switching Speed |

|--------|------------------|-----------------|

| BJT    | Medium           | Medium          |

| MOSFET | Low              | Fast            |

| GTO    | High             | Slow            |

| IGBT   | Medium           | Medium          |

| MCT    | Medium           | Medium          |

Figure 4: Device operating regions: Voltage vs Frequency (Rashid 2001:64)

This figure indicates that a categorization based on voltage and switching frequency provides two key parameters for determining whether a BJT, a MOSFET or an IGBT is the better device in an application (Rashid 2001:64). In addition to improvements in these devices, the progress in semiconductor technology will undoubtedly lead to

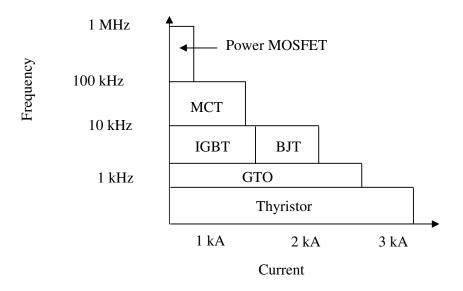

higher power ratings (Rashid 2001:64). Figure 5 is the categorization based on current and switching frequency for determining the device application. However, there are still difficulties in selecting a component for use in the crossover region, which includes voltages of 250 V to 1000 V and frequencies of 20 kHz to 100 kHz. At voltages < 1000 V, the BJT has been entirely replaced by the MOSFET and at higher voltages new designs use IGBTs (Rashid 2001:64).

Figure 5: Device operating regions: Current vs Frequency (Rashid 2001:64)

On the other hand, the forced-commutated thyristor, which was once widely used in circuits for controllable switch applications, is no longer being used in new converter designs with the possible exception of power converters in multi-MVA ratings. This is just a pertinent example of how the advances in semiconductor power devices have modified converter design (Mohan *et al.* 2003:29).

#### 2.4 Power Modules

The demand to control the electric power in electric motor drive systems and industrial controls existed for many years. This led to the early development of the Ward-Leonard system to obtain a variable DC voltage for the control of DC motor

drives. Power electronics have revolutionized the concept of power control for power conversion and for control of electrical motor drives (Rashid 2004:1).

According to Rashid (2004:26) power devices are available as a single unit or in a module. A power converter often requires two, four or six devices, depending on its topology. Power modules with dual (half-bridge configuration) or quad (full-bridge) or six (for three-phase) devices are available for almost all types of power devices (Galvez, Jorda, Vellvehi, Millan, Jose-Prieto & Martin 2007:1).

Mohan *et al.* (2003:656) classifies this as an intelligent module or also known as smart power. According to Gadi (1995:33) these modules are being used in power electronics technology and can be viewed as a box that interfaces a power source to any load as shown in Figure 6.

Figure 6: Generalized power converter system (Gadi 1995:33)

The modules offer the advantages of lower ON-state losses, high voltage and current switching characteristics and higher speeds than that of conventional or discrete devices. Some modules even include transient protection and gate drive circuitry (Rashid 2004:26).

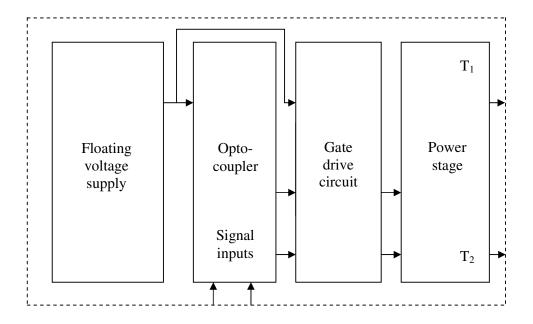

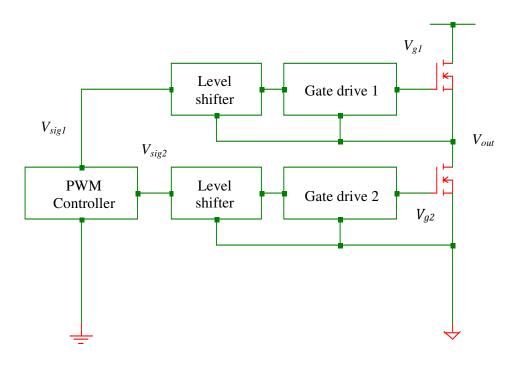

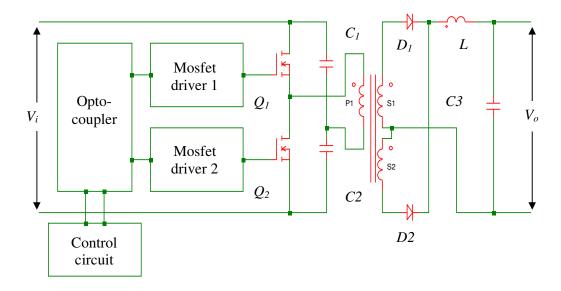

#### 2.4.1 Structure of the bidirectional switch power module

The universal bidirectional galvanic isolated switch module basically consists of power switches in a bidirectional switch function (bidirectional in current and voltage) and these power devices are connected in common emitter configuration (Galvez *et al.* 2007:3). It includes the power transistors gate drivers in a totem-pole configuration for driving MOSFETs, galvanic isolation between control and power stages, over-voltage protection devices and floating voltage power supply (Wheeler, Clare, Empringham, Bland & Apap 2002:384).

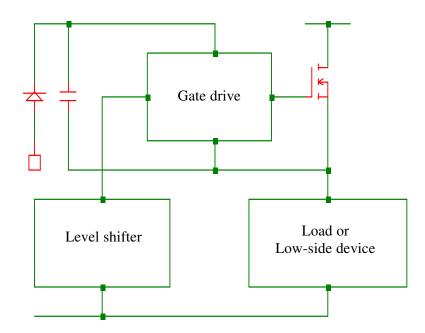

Gate drive circuits are commercially available to drive individual devices or modules (Rashid 2004:26). Intelligent modules can be classified as state-of-the-art power electronics, which integrate the power module and the peripheral circuit as shown in Figure 7 (Galvez *et al.* 2007:3). The user needs only to connect external power supplies (Kularatna 2008:129-132).

According to Rashid (2004:27) analogue circuits are used for creating the sensors necessary for self-protection and for providing a rapid feedback loop, which can terminate chip operation harmlessly when the system conditions exceed the normal operation conditions. For example, smart power or power module chips must be designed to shutdown without damage when a short circuit occurs across a load such as a motor winding (Romero, Fusaro & Martinez 1995:918).

Baliga (1996:35) states that in smart power technology, the load current is monitored and whenever this current exceeds a preset limit, the drive voltage to the power switches is shut OFF. In addition to this, features such as over-current protection, overvoltage and over-temperature protection are commonly included to prevent destructive failures (Rashid 2004:27). Power modules allow the control of output voltages and also allow obtaining better quality of the output current waveforms because the required commutation times between the power switches can be minimized (Rashid 2004:27). These classical circuits do not show natural free-wheeling paths for the inductive load currents.

Figure 7: Power switch module shown in block diagram (Galvez et al. 2007:3)

Thus, current commutation strategy between power switches is of main importance in order to ensure correct performances and high reliability (Mulvey, Salim & Carr 1998:57). These algorithms determine the right switching sequence of the different transistors and their delay times. And these delays are mainly related to the characteristic switching times of the power devices (Galvez *et al.* 2007:1).

#### 2.4.2 Operation of the switch module

The control circuitry determines the turn-ON and turn-OFF instants of the bidirectional switches using relatively complex modulation algorithms to fix the current and voltage target values in the load. The processed high-level logic control signals are galvanically isolated using opto-couplers before application to the power transistors' gate-drivers. The floating voltage supply of these drivers is supplied by an integrated DC-DC converter. The gate control signals are finally sent to the power devices and other protection devices such as over-voltage transient suppressors and gate resistors (Galvez *et al.* 2007:1).

#### 2.4.3 Bidirectional switches

According to Casadei, Serra, Tani & Zarri (2005:83) several studies were conducted to come up with the necessary bidirectional switches for the power modules. The bidirectional switches were initially obtained by combining discrete components. Then, as the interest towards modules increased, some manufacturers produced power modules specifically designed for the application (Casadei Serra, Tani & Zarri 2002(a):371). The switches are usually traditional silicon IGBTs, but may also have device types such as MCTs and MOSFETs with SiC diodes (Wheeler, Clare & Empringham 1998(b):708).

Casadei *et al.* (2002(b):1110) also point out that power modules require bidirectional switches with the capability to block the voltage and to conduct current in both directions. There are two main topologies for bidirectional switches, namely the common-emitter anti-parallel configuration and the common-collector anti-parallel configuration (Casadei *et al.* 2005:86). The common-emitter configuration is represented in Figure 8. As shown, two IGBTs are connected with two diodes in an anti-parallel configuration. The diodes provide the reverse blocking capability.

Figure 8: Bidirectional switches in common-emitter configuration (Casadei *et al.* 2005:1-86)

The main advantage of this solution is that the two IGBTs can be driven with respect to the same point, i.e. the same common emitter, that can be considered as a local ground for the bidirectional switch (Wheeler, Clare & Empringham 1998(a):627). The common-collector arrangement is presented in Figure 9, where two IGBTs are now arranged in a common-collector configuration and their collector terminals are at common point which can be considered as the ground point (Casadei *et al.* 2005:86).

Figure 9: Bidirectional switches in common-collector configuration (Casadei *et al.* 2005:1-86)

Wheeler and Grant (1997:54) point out that the two diodes used with IGBTs in common emitter configuration provide the reverse-voltage blocking capability; whereas MOSFETs have the internal body diodes that provide the reverse-voltage blocking capability. This facility can then be used to reduce the switching losses during commutation of the load current (Casadei *et al.* 2002(a):371).

#### 2.5 Power semiconductor devices

Rashid (2004:9) categorizes power transistors as four types; the BJT, IGBTs, SITs and power MOSFETs. One of the main important performance features of any semiconductor switching device is its switching characteristics. Understanding the device switching characteristics greatly improves its utilisation in the various applications. Power semiconductor devices have three operating states commonly known as the cut-OFF mode, the active mode and the saturation mode (Mohan *et al.* 2003:20). Where power electronic converters utilise switch-mode operation devices

are operated in either the cut-OFF region or the saturation region, whilst making the transition through the active or linear region as short as possible in order to facilitate maximum power conversion efficiency (Khan 2007:544).

According to Rashid (2001:83) in order to achieve these fast transition times, a suitable gate-driver circuit is required. This gate-driver has to be able to supply the necessary charge to the power semiconductor device gate junction in order to achieve turn-ON and turn-OFF as fast as possible. Power semiconductors can be classified into two categories with respect to drive requirements, namely:

- current-driven devices and

- voltage-driven devices.

Only voltage-driven devices will be looked at in this regard owing to BJTs being replaced by MOSFETs and IGBTs which are both voltage-driven devices.

#### 2.5.1 Voltage-controlled devices

These devices are semiconductors which require a constant voltage drive on the gate control terminal in order to remain in conduction. The input drive requirements of these devices are substantially lower than their current-driven counter parts and are the preferred choice in modern power electronics. Two such devices are the MOSFET and the IGBT which are forced commutated switching devices being fully controlled at the gate terminal under normal operating conditions (Khan 2007:544).

The gate input junction of the MOSFET and IGBT is purely capacitive, so no gate drive current is needed in the steady state, unlike other transistors. A minimum gate drive voltage however must be maintained (above the gate threshold voltage) at the device gate in order for it to remain in conduction (Khan 2007:544). For the MOSFET to carry drain current, a channel between the drain and the source must be created. This can only occur when the continuous application of a gate-to-source voltage exceeds the device threshold voltage  $V_{Th}$  (Whittington, Flynn & Macpherson 1997:120). The device can then be either in the triode region, which is also called

'constant resistance region', or in the saturation region depending on the value of  $V_{DS}$  (Rashid 2001: 83). A high current low impedance drive circuit is needed to inject or remove current, from the gate with high slew rates in order to switch the device rapidly. The gate drain capacitance, although small, can also require significant charge at high drain voltage slew rates (Khan 2007:544).

#### 2.6 Theoretical overview of MOSFETs

Because of their high efficiency, power MOSFETs and IGBTs are considered ideal as semiconductor switches and are ranked as one of the most significant developments in power electronics (Swart 2004(a):40). According to Rashid (2001:80) the ability of high power MOSFETs to act as switches make them the ideal switching devices and they are one of the fastest power switching devices with voltage power ratings up to 1500 V and current rating as high as 100 A.

This statement is largely attributed to the numerous advantages that the MOSFET holds over other semiconductor devices. Some noteworthy advantages are (Swart 2004(a):40):

- High switching speeds and

- Their ability to maintain gain up to much higher frequencies.

In the ON-state the voltage across the switch should ideally be zero, independent of the current. In the OFF-state the opposite must hold true with zero current flowing independent of the voltage (Swart 2004(a):40). Modern power MOSFETs also have an internal body diode connected between the source and the drain as shown in Figure 10, which provides a reverse direction for the drain current allowing a bidirectional switch implementation (Rashid 2001:82). Even though they do have adequate current and switching speed ratings, in some applications that require the use of ultra-fast diodes, an external fast recovery diode is added in anti-parallel fashion after blocking the body diode by a slow recovery as shown in Figure 11 (Rashid 2001:82).

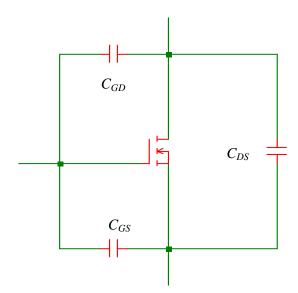

According to (Agrawal 2001:116) another important parameter that affects the MOSFET switching behavior is the parasitic capacitances between the device's three terminals, namely, gate-to-source ( $C_{GS}$ ), gate-to-drain ( $C_{GD}$ ) and drain-to-source ( $C_{DS}$ ) capacitances.

Figure 10: MOSFET internal body diode (Rashid 2001:82)

Figure 11: Implementation of a fast recovery body diode (Rashid 2001:82)

Normally, manufacturer's data sheets do not specify these device capacitances rather they quote input, output and reverse common source capacitances ( $C_{ISS}$ ,  $C_{OSS}$ , and  $C_{RSS}$  respectively) as shown in Figure 12.

All these capacitances are related according to the following:

$$C_{GD} = C_{RSS}$$

$$C_{GS} = C_{ISS} - C_{RSS}$$

$$C_{DS} = C_{OSS} - C_{RSS}$$

(2)

Where:

$C_{RSS} \equiv \text{small-signal reverse transfer capacitance in pF}$

$C_{ISS} \equiv \text{small-signal input capacitance}$  with the drain and source terminals shorted in pF

$C_{OSS} \equiv \text{small-signal output capacitance with the gate and source terminals shorted in pF (Rashid 2001:83).}$

Figure 12: Equivalent MOSFET representation including junction capacitances (Rashid 2001:83)

#### 2.6.1 Safe Operation Area

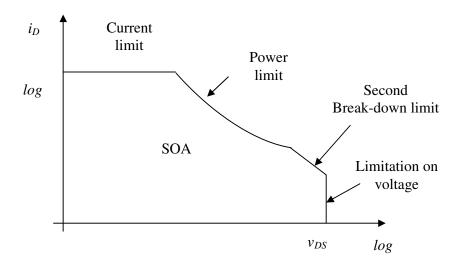

According to Mohan *et al.* (2003:591) MOSFETs have a safe operation area (SOA) that provides the current and voltage limits which the device is able to handle without destructive failure. A typical SOA graph for a MOSFET device is shown in Figure 13. As the drain-source voltage starts increasing, the device starts leaving the ON-state and enters the saturation region. During the transition time the device exhibits a large voltage and current simultaneously. The maximum current limit while the device is ON is determined by the maximum power dissipation ( $P_{dis}$ ) equation (3) (Kazimierczuk 2008:685).

$$P_{dis} = I_D^2 \times R_{DS(ON)} \quad W \tag{3}$$

Where:

$R_{(DS)ON} \equiv$  on-resistance of the MOSFET in  $\Omega$  $I_D \equiv$  forward current in A

Figure 13: A typical graph for safe operation areas (SOA) (Mohan *et al.* 2003:591)

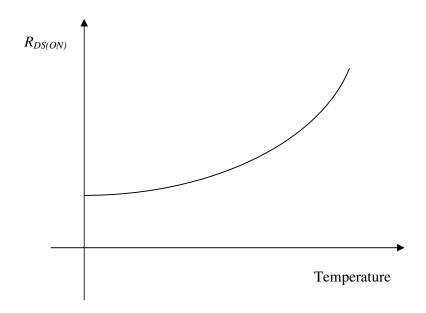

Mohan *et al* (2003:591) further states that at higher drain-source voltage values that approach the avalanche breakdown, it is observed that a power MOSFET suffers from a second breakdown phenomenon. The second breakdown occurs when the MOSFET is in the blocking state (OFF) and further increase in  $V_{DS}$  will cause a sudden drop in the blocking voltage (Whittington *et al.* 1997:125). According to Rashid (2001:91) the source of this phenomenon in a MOSFET is caused by the presence of a parasitic n-type bipolar transistor. Furthermore commercial MOSFETs and IGBTs have excellent high operating temperatures and the effect of temperature is more prominent on the ON-state resistance as shown in Figure 14 (Rashid 2001:91).

Figure 14: On-state resistance against temperature (Rashid 2001: 92)

As the ON-state resistance increases, the conduction losses also increase. This large  $V_{DS}$  limits the use of MOSFETs in high-voltage applications. Maximum drain current, the breakdown voltage and the internal junction temperature governed by the power dissipation in the device are the factors that determine the safe operating area of the devices (Mohan *et al* 2003:591). The use of silicon carbide instead of silicon has reduced the effect of this drain-to-source voltage ( $V_{DS}$ ) many fold (Culurciello, Pouliquen, Andreou, Strohbehn & Jaskulek 2005:138).

#### 2.6.2 Gate voltage limitations

The silicon oxide layer between the gate and the source regions can be punctured by exceeding its dielectric strength (Whittington *et al.* 1997:125). From the data sheet the gate-to-source voltage is between 10 V and 30 V for most devices (Philips Semiconductor Devices 2004:7). Care should be exercised not to exceed the gate-to-source maximum voltage rating. Even if the applied gate voltage is kept below the maximum rated gate voltage, the stray inductance of the gate connection coupled with the gate capacitance may generate ringing voltages that could lead to the destruction of the oxide layer. Over-voltages can also be coupled through the draingate self-capacitance owing to transients in the drain circuit. A gate drive circuit with very low impedance insures that the gate voltage is not exceeded in normal operation (Whittington *et al.* 1997:125).